Loading...

Testbench Code

`timescale 1ns/1ps

module tb_mux4to1;

// ========= Inputs / Outputs =========

reg d0, d1, d2, d3;

reg [1:0] sel;

wire y;

// ========= Expected + mismatch =========

reg expected_y;

wire mismatch = (y !== expected_y);

// ========= Counters =========

integer TOTAL_TEST_CASES = 0;

integer TOTAL_PASSED_TEST_CASES = 0;

integer TOTAL_FAILED_TEST_CASES = 0;

// ========= DUT =========

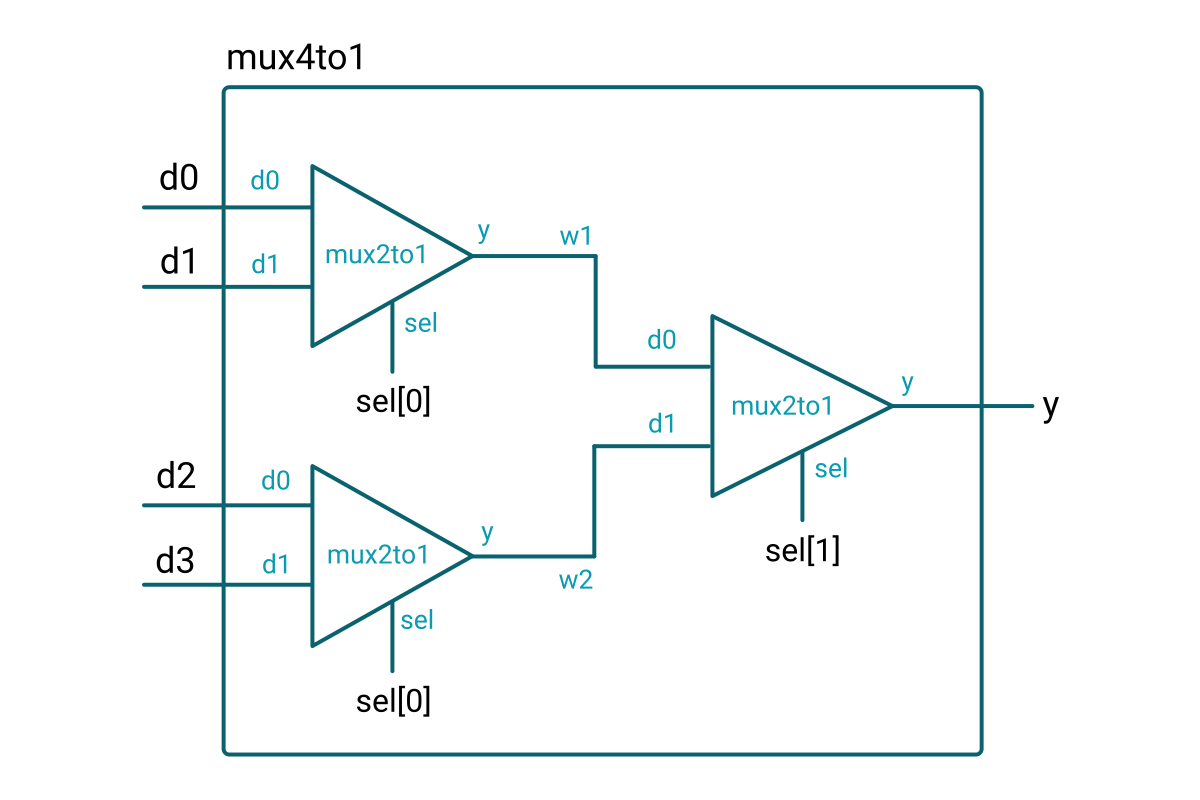

mux4to1 dut (

.d0(d0), .d1(d1), .d2(d2), .d3(d3),

.sel(sel),

.y(y)

);

// ========= VCD: dump only I/O, expected, mismatch =========

initial begin

$dumpfile("tb_mux4to1.vcd");

$dumpvars(0,

tb_mux4to1.d0,

tb_mux4to1.d1,

tb_mux4to1.d2,

tb_mux4to1.d3,

tb_mux4to1.sel,

tb_mux4to1.y,

tb_mux4to1.expected_y,

tb_mux4to1.mismatch

);

end

// ========= Golden model =========

task compute_expected;

input t_d0, t_d1, t_d2, t_d3;

input [1:0] t_sel;

begin

case (t_sel)

2'b00: expected_y = t_d0;

2'b01: expected_y = t_d1;

2'b10: expected_y = t_d2;

2'b11: expected_y = t_d3;

endcase

end

endtask

// ========= Exhaustive run with counters =========

integer s, d;

initial begin

$display("sel d0 d1 d2 d3 | y | expected_y | mismatch");

for (s = 0; s < 4; s = s + 1) begin

for (d = 0; d < 16; d = d + 1) begin

{d0, d1, d2, d3} = d[3:0];

sel = s[1:0];

compute_expected(d0, d1, d2, d3, sel);

#1; // settle

// Update counters

TOTAL_TEST_CASES = TOTAL_TEST_CASES + 1;

if (!mismatch)

TOTAL_PASSED_TEST_CASES = TOTAL_PASSED_TEST_CASES + 1;

else

TOTAL_FAILED_TEST_CASES = TOTAL_FAILED_TEST_CASES + 1;

// Per-vector line (inputs -> y -> expected_y -> mismatch)

$display("%02b %b %b %b %b | %b | %b | %b",

sel, d0, d1, d2, d3, y, expected_y, mismatch);

end

end

// ========= Summary =========

$display("======================================");

$display("TOTAL_TEST_CASES=%0d", TOTAL_TEST_CASES);

$display("TOTAL_PASSED_TEST_CASES=%0d", TOTAL_PASSED_TEST_CASES);

$display("TOTAL_FAILED_TEST_CASES=%0d", TOTAL_FAILED_TEST_CASES);

$display("ALL_TEST_CASES_PASSED=%s",

(TOTAL_FAILED_TEST_CASES==0) ? "true" : "false");

$display("======================================");

$finish;

end

endmodule