9. XOR Gate Using Basic Gates

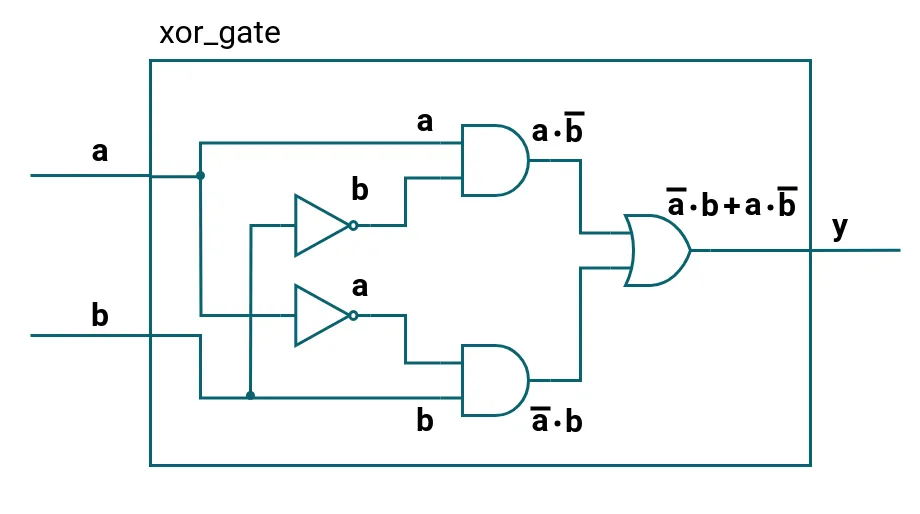

Design a XOR gate (xor_gate) using basic gates (and_gate, or_gate, not_gate).

Requirements

- Module name:

xor_gate - Inputs:

a, b(1-bit each) - Output:

y(1-bit)

Notes

- You must build

xor_gatestructurally by instantiating smaller gate modules (and_gate,or_gate,not_gate). - Do not use Verilog’s built-in

^operator. Use the Boolean equation for XOR:

y=(a⋅b')+(a'⋅b)

Truth Table

| a | b | y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |